Texas Instruments

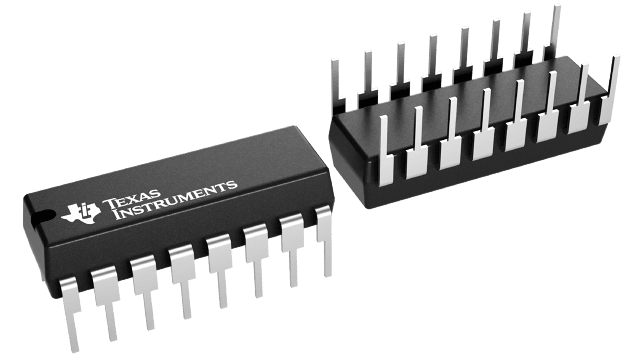

CD74HCT670E

CD74HCT670E

Couldn't load pickup availability

CD74HCT670E Texas Instruments - Yeehing Electronics

High Speed CMOS Logic 4-by-4 Register File

Pricing (USD)

| Quantity | Unit Price |

| 1 — 99 | 8.006 |

| 100 — 249 | 6.527 |

| 250 — 999 | 5.13 |

| 1,000 + | 3.05 |

The above prices are for reference only.

Specifications

| Manufacturer | Texas Instruments |

| Product Category | Registers |

| RoHS | Y |

| Logic Type | CMOS |

| Logic Family | HCT |

| Number of Circuits | Single |

| Propagation Delay Time | 50 ns |

| High Level Output Current | - 6 mA |

| Low Level Output Current | 6 mA |

| Supply Voltage - Max | 5.5 V |

| Supply Voltage - Min | 4.5 V |

| Minimum Operating Temperature | - 55 C |

| Maximum Operating Temperature | + 125 C |

| Package / Case | PDIP-16 |

| Packaging | Tube |

| Function | Register File |

| Height | 4.57 mm |

| Input Type | Single-Ended |

| Length | 19.3 mm |

| Output Type | 3-State |

| Series | CD74HCT670 |

| Width | 6.35 mm |

| Brand | Texas Instruments |

| Mounting Style | Through Hole |

| Number of Channels | 4 |

| Number of Input Lines | 4 |

| Number of Output Lines | 4 |

| Operating Supply Voltage | 4.5 V to 5.5 V |

| Polarity | Non-Inverting |

| Product Type | Registers |

| Factory Pack Quantity | 25 |

| Subcategory | Logic ICs |

| Unit Weight | 0.033570 oz |

For more information, please refer to datasheet

Documents

| CD74HCT670E Datasheet |

More Information

The HC670 and CD74HCT670 are 16-bit register files organized as 4 words x 4 bits each. Read and write address and enable inputs allow simultaneous writing into one location while reading another. Four data inputs are provided to store the 4-bit word. The write address inputs (WA0 and WA1) determine the location of the stored word in the register. When write enable (WE) is low the word is entered into the address location and it remains transparent to the data. The outputs will reflect the true form of the input data. When (WE) is high data and address inputs are inhibited. Data acquisition from the four registers is made possible by the read address inputs (RA1 and RA0). The addressed word appears at the output when the read enable (RE) is low. The output is in the high impedance state when the (RE) is high. Outputs can be tied together to increase the word capacity to 512 x 4 bits.