Texas Instruments

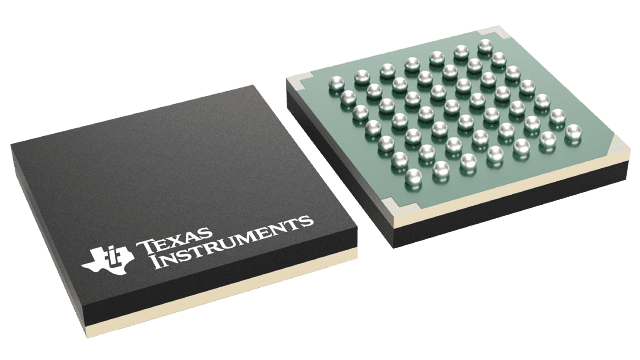

SCAN921224SLC/NOPB

SCAN921224SLC/NOPB

Couldn't load pickup availability

SCAN921224SLC/NOPB Texas Instruments - Yeehing Electronics

20 to 66-MHz 10-bit deserializer with IEEE 1149.1 test access

Pricing (USD)

| Quantity | Unit Price |

| 1 — 99 | 8.977 |

| 100 — 249 | 7.319 |

| 250 — 999 | 5.752 |

| 1,000 + | 3.42 |

The above prices are for reference only.

Specifications

| Manufacturer | Texas Instruments |

| Product Category | Serializers & Deserializers - Serdes |

| RoHS | Y |

| Type | Deserializer |

| Data Rate | 660 Mb/s |

| Input Type | LVDS |

| Output Type | LVTTL |

| Number of Inputs | 1 Input |

| Number of Outputs | 10 Output |

| Operating Supply Voltage | 3.3 V |

| Minimum Operating Temperature | - 40 C |

| Maximum Operating Temperature | + 85 C |

| Mounting Style | SMD/SMT |

| Package / Case | FBGA-49 |

| Packaging | Tray |

| Height | 1.04 mm |

| Length | 7 mm |

| Series | SCAN921224 |

| Width | 7 mm |

| Brand | Texas Instruments |

| Moisture Sensitive | Yes |

| Operating Supply Current | 90 mA |

| Pd - Power Dissipation | 1.47 W |

| Product Type | Serializers & Deserializers - Serdes |

| Factory Pack Quantity | 416 |

| Subcategory | Interface ICs |

| Supply Voltage - Max | 3.6 V |

| Supply Voltage - Min | 3 V |

| Unit Weight | 0.014110 oz |

For more information, please refer to datasheet

Documents

| SCAN921224SLC/NOPB Datasheet |

More Information

The SCAN921023 transforms a 10-bit wide parallel LVCMOS/LVTTL data bus into a single high speed Bus LVDS serial data stream with embedded clock. The SCAN921224 receives the Bus LVDS serial data stream and transforms it back into a 10-bit wide parallel data bus and recovers parallel clock. Both devices are compliant with IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture with the incorporation of the defined boundary-scan test logic and test access port consisting of Test Data Input (TDI), Test Data Out (TDO), Test Mode Select (TMS), Test Clock (TCK), and the optional Test Reset (TRST). IEEE 1149.1 features provide the designer or test engineer access to the backplane or cable interconnects and the ability to verify differential signal integrity to enhance their system test strategy. The pair of devices also features an at-speed BIST mode which allows the interconnects between the Serializer and Deserializer to be verified at-speed.