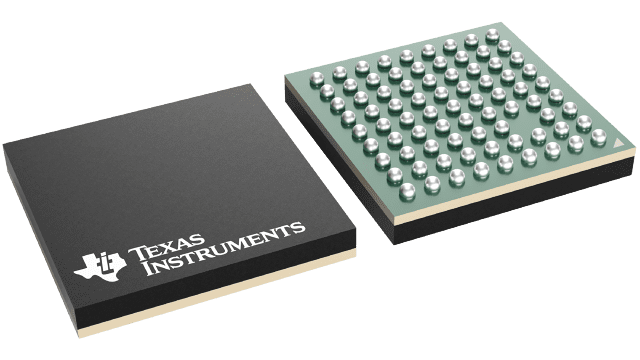

Texas Instruments

SN65LVDS302ZXHR

SN65LVDS302ZXHR

Couldn't load pickup availability

SN65LVDS302ZXHR Texas Instruments - Yeehing Electronics

Programmable 27-bit display serial interface receiver

Pricing (USD)

| Quantity | Unit Price |

| 1 — 99 | 2.02 |

| 100 — 249 | 1.77 |

| 250 — 999 | 1.241 |

| 1,000 + | 0.70 |

The above prices are for reference only.

Specifications

For more information, please refer to datasheet

Documents

| SN65LVDS302ZXHR Datasheet |

More Information

The SN65LVDS302 receiver de-serializes FlatLink™3G compliant serial input data to 27 parallel data outputs. The SN65LVDS302 receiver contains one shift register to load 30 bits from 1, 2 or 3 serial inputs and latches the 24 pixel bits and 3 control bits out to the parallel CMOS outputs after checking the parity bit. If the parity check confirms correct parity, the Channel Parity Error (CPE) output remains low. If a parity error is detected, the CPE output generates a high pulse while the data output bus disregards the newly-received pixel. Instead, the last data word is held on the output bus for another clock cycle.